Résultats de la recherche pour "risc OR v OR assembly OR language OR programming OR using OR esp32 OR c3 OR and OR qemu"

-

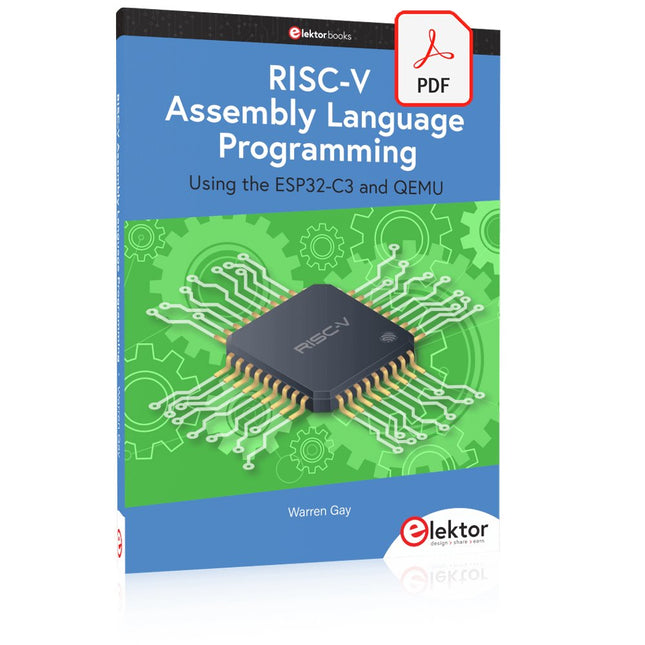

Elektor Digital RISC-V Assembly Language Programming using ESP32-C3 and QEMU (E-book)

With the availability of free and open source C/C++ compilers today, you might wonder why someone would be interested in assembler language. What is so compelling about the RISC-V Instruction Set Architecture (ISA)? How does RISC-V differ from existing architectures? And most importantly, how do we gain experience with the RISC-V without a major investment? Is there affordable hardware available? The availability of the Espressif ESP32-C3 chip provides a way to get hands-on experience with RISC-V. The open sourced QEMU emulator adds a 64-bit experience in RISC-V under Linux. These are just two ways for the student and enthusiast alike to explore RISC-V in this book. The projects in this book are boiled down to the barest essentials to keep the assembly language concepts clear and simple. In this manner you will have “aha!” moments rather than puzzling about something difficult. The focus in this book is about learning how to write RISC-V assembly language code without getting bogged down. As you work your way through this tutorial, you’ll build up small demonstration programs to be run and tested. Often the result is some simple printed messages to prove a concept. Once you’ve mastered these basic concepts, you will be well equipped to apply assembly language in larger projects.

€ 34,95

Membres € 27,96

-

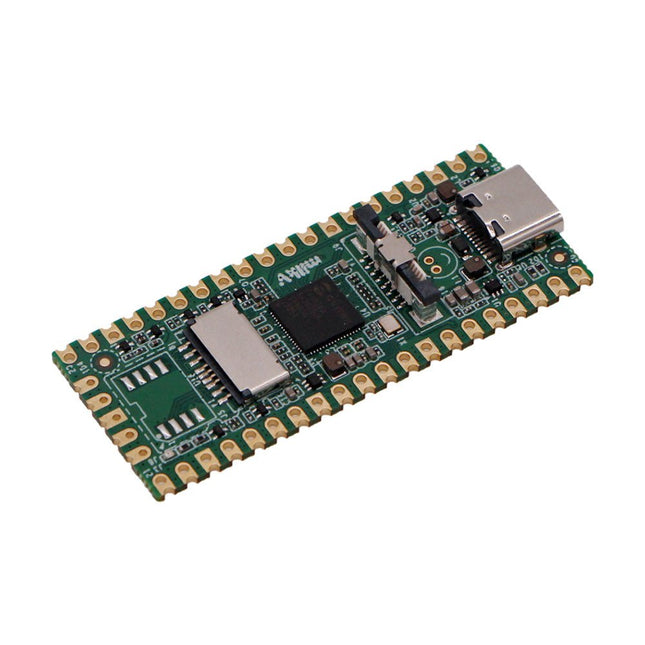

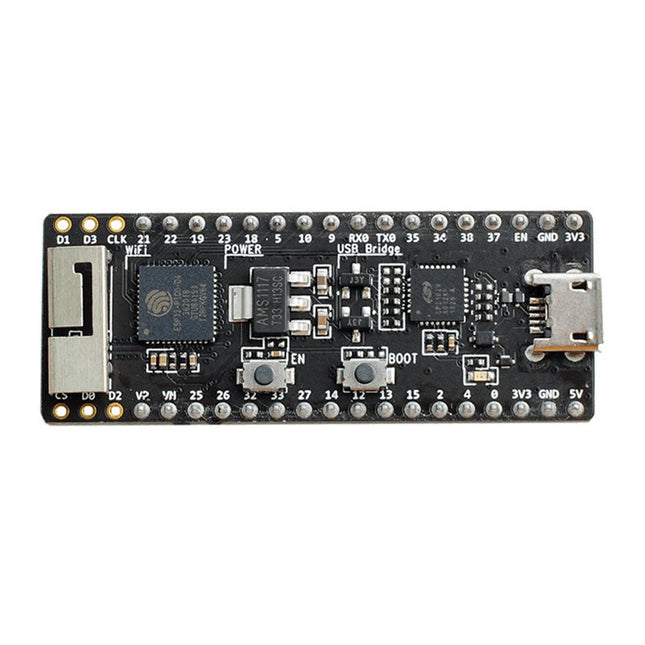

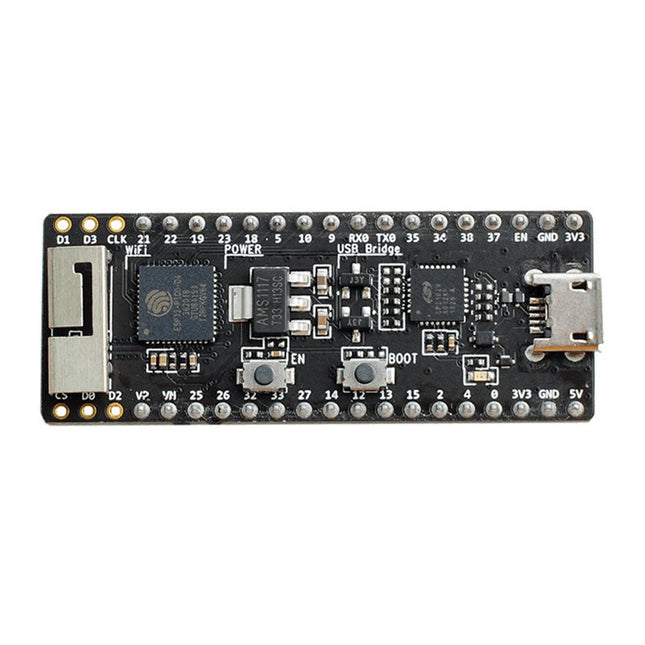

Espressif ESP32-C3-DevKitM-1

ESP32-C3-DevKitM-1 est une carte de développement d'entrée de gamme basée sur l'ESP32-C3-MINI-1, un module nommé pour sa petite taille. Cette carte intègre des fonctions Wi-Fi et Bluetooth LE complètes. La plupart des broches d'E/S du module ESP32-C3-MINI-1 sont réparties sur les connecteurs des deux côtés de la carte pour faciliter l'interfaçage. Les développeurs peuvent soit connecter les périphériques avec des fils de liaison, soit monter l'ESP32-C3-DevKitM-1 sur une plaque d’expérimentation. Caractéristiques ESP32-C3-MINI-1 L'ESP32-C3-MINI-1 est un module polyvalent Wi-Fi et Bluetooth LE, livré avec une antenne sur circuit imprimé. Au cœur de ce module se trouve la puce ESP32-C3FN4, qui intègre une mémoire flash de 4 Mo. La flash étant intégrée à la puce ESP32-C3FN4 plutôt qu'au module, le module ESP32-C3-MINI-1 est plus petit. 5 V à 3,3 V LDO Régulateur de tension qui convertit une alimentation de 5 V en une tension de 3,3 V. 5 V LED de mise sous tension S'allume lorsque l'alimentation USB est connectée à la carte. Tête de broche Toutes les broches GPIO disponibles (à l'exception du bus SPI pour la flash) sont réparties sur les connecteurs d’extension de la carte. Pour plus de détails, veuillez consulter le bloc d'en-tête. Bouton Boot Bouton de téléchargement. En maintenant la touche Boot enfoncée, puis en appuyant sur Reset, vous passez en mode de téléchargement de micrologiciel pour télécharger le micrologiciel via le port série. Port Micro-USB Interface USB. Alimentation de la carte ainsi que de l'interface de communication entre un ordinateur et la puce ESP32-C3FN4. Bouton de réinitialisation Appuyez sur ce bouton pour redémarrer le module. Pont USB/UART Une seule puce de pont USB-UART fournit des taux de transfert allant jusqu'à 3 Mbps. LED RVB LED RVB adressable, pilotée par GPIO 8. Téléchargements ESP32-C3 Datasheet ESP32-C3-MINI-1 Datasheet ESP32-C3-DevKitM-1 Schematic ESP32-C3-DevKitM-1 PCB Layout ESP32-C3-DevKitM-1 Dimensions

€ 19,95€ 7,98

Membres identique

-

Espressif ESP32-C3-WROOM-02U-N4

L’ESP32-C3-WROOM-02U est un module Wi-Fi et Bluetooth LE. La richesse de ses périphériques et ses hautes performances, en font un choix idéal pour la domotique, les automatismes industriels, les applications médicales, l’électronique grand-public, etc. L’ESP32-C3-WROOM-02U comprend une mémoire flash externe SPI et un connecteur pour une antenne extérieure. La température ambiante de fonctionnement de l ’ESP32-C3-WROOM-02U, utilisant un chip ESP32-C3, s’étend de –40 à 85°C. L’ESP32-C3 possède un processeur 32-bit RISC-V à un cœur. Il intègre un ensemble important de périphériques, comprenant une liaison UART, un bus I²C, une interface I²S, des périphériques de contrôle à distance, un contrôleur LED PWM (ou MLI, Modulation de Largeur d’Impulsion), un contrôleur DMA générique, un contrôleur TWAI, un contrôleur USB série / JTAG, un capteur de température, un convertisseur CAN, etc. Il offre également des interfaces SPI, Dual SPI and Quad SPI. Caractéristiques Mémoire Flash : 4 Mo (Quad SPI) Dimensions : 18,0 x 20,0 x 3,2 mm Téléchargements Datasheet

€ 7,95€ 3,18

Membres identique

-

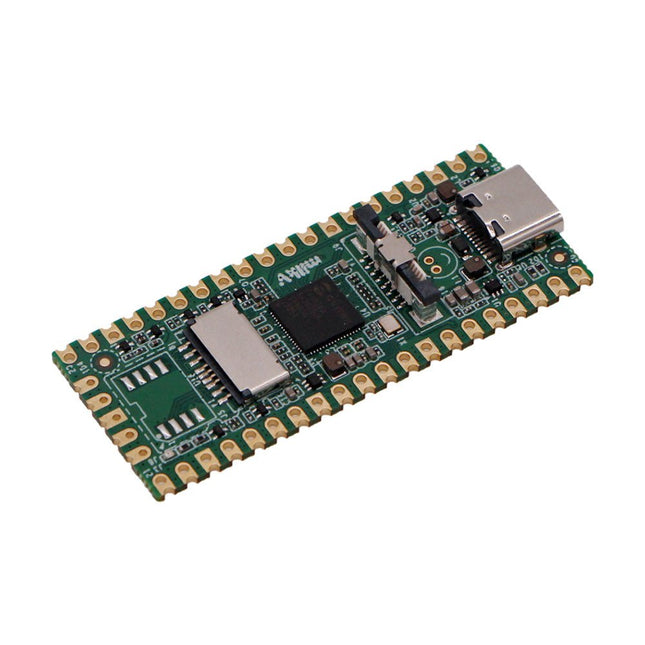

milkV Milk-V Duo 256M RISC-V Ordinateur monocarte

Le Milk-V Duo 256M est une plateforme de développement embarquée ultra-compacte basée sur la puce SG2002. Il peut exécuter Linux et RTOS, fournissant ainsi une plate-forme fiable, peu coûteuse et hautes performances pour les professionnels, les ODM industriels, les passionnés d'AIoT, les bricoleurs et les créateurs. Cette carte est une version améliorée de Duo avec une augmentation de mémoire à 256 Mo, destinée aux applications exigeant des capacités de mémoire plus importantes. Le SG2002 élève la puissance de calcul à 1,0 TOPS @ INT8. Il permet une commutation transparente entre les architectures RISC-V/ARM et prend en charge le fonctionnement simultané de deux systèmes. De plus, il comprend une gamme d'interfaces GPIO riches telles que SPI, UART, adaptées à un large éventail de développements matériels dans la surveillance intelligente de pointe, notamment des caméras TIP, des judas intelligents, des sonnettes visuelles, et bien plus encore. SG2002 est une puce hautes performances à faible consommation conçue pour divers domaines de produits tels que les caméras IP de surveillance intelligente de pointe, les serrures de porte intelligentes, les sonnettes visuelles et l'intelligence domestique. Il intègre la compression et le décodage vidéo H.264, l'encodage de compression vidéo H.265 et les capacités du FAI. Il prend en charge plusieurs algorithmes d'amélioration et de correction d'image tels que la large plage dynamique HDR, la réduction du bruit 3D, le désembuage et la correction de la distorsion de l'objectif, offrant aux clients une qualité d'image vidéo de qualité professionnelle. La puce intègre également un TPU auto-développé, offrant une puissance de calcul de 1,0 TOPS pour des opérations sur des nombres entiers de 8 bits. Le moteur de planification TPU spécialement conçu fournit efficacement un flux de données à large bande passante pour tous les cœurs de l'unité de traitement tensoriel. De plus, il offre aux utilisateurs un puissant compilateur de modèles d’apprentissage en profondeur et un kit de développement de SDK logiciels. Les principaux frameworks d'apprentissage profond tels que Caffe et Tensorflow peuvent être facilement portés sur sa plate-forme. En outre, il inclut le démarrage de sécurité, les mises à jour sécurisées et le cryptage, fournissant une série de solutions de sécurité allant du développement à la production de masse jusqu'aux applications de produits. La puce intègre un sous-système MCU 8 bits, remplaçant le MCU externe typique pour atteindre les objectifs d'économie de coûts et d'efficacité énergétique. Spécifications SoC SG2002 RISC-V CPU C906 @ 1 Ghz + C906 @ 700 MHz Arm CPU 1x Cortex-A53 @ 1 GHz MCU 8051 @ 6 Ko SRAM Mémoire 256 Mo de DRAM SIP TPU 1.0 TOPS @ INT8 Stockage 1x Connecteur microSD ou 1x SD NAND intégré USB 1x USB-C pour l'alimentation et les données, USB Pads disponibles CSI 1x Connecteur FPC 16P (MIPI CSI 2 voies) Prise en charge des capteurs 5 M @ 30 ips Ethernet Ethernet 100 Mbit/s avec PHY Audio Via des pads GPIO GPIO Jusqu'à 26x pads GPIO Puissance 5 V/1 A Support du système d'exploitation Linux, RTOS Dimensions 21 x 51 mm Téléchargements Documentation GitHub

€ 32,95€ 13,18

Membres identique

-

Elektor Digital Assembly Language Essentials (E-book)

A Guide to Powerful Programming for Embedded Systems You must be a well-rounded professional to excel in the ever-evolving, rapidly developing embedded design and programming industry. Simply put, when it comes to electronics design and programming, the more topics you can master, the more you’ll flourish at your workplace and at your personal workbench. This shouldn’t be a surprise, as the line between the skills of a hardware engineer and software engineer is blurring. The former should have a good grasp of programming in order to build efficient systems. The latter should understand the details of the design (whether it’s a physical or virtual application) for which he or she is writing code. Thus, to be successful, a modern professional electronics engineer must have a solid grasp of both hardware design and programming. Assembly Language Essentials is a matter-of-fact guide to Assembly that will introduce you to the most fundamental programming language of a processor. Unlike other resources about Assembly that focus exclusively on specific processors and platforms, this book uses the architecture of a fictional processor with its own hardware and instruction set. This enables you to consider the importance of Assembly language without having to deal with predetermined hardware or architectural restrictions. You’ll immediately find this thorough introduction to Assembly to be a valuable resource, whether you know nothing about the language or you have used it before. The only prerequisite is that you have a working knowledge of at least one higher-level programming language, such as C or Java. Assembly Language Essentials is an indispensible resource for electronics engineering professionals, academics, and advanced students looking to enhance their programming skills. The book provides the following, and more: An introduction to Assembly language and its functionality Significant definitions associated with Assembly language, as well as essential terminology pertaining to higher-level programming languages and computer architecture Important algorithms that may be built into high-level languages, but must be done the “hard way” in Assembly language — multiplication, division, and polynomial evaluation A presentation of Interrupt Service Routines with examples A free, downloadable Assembler program for experimenting with Assembly

€ 29,95

Membres € 23,96

-

Elektor Digital Explore ATtiny Microcontrollers using C and Assembly Language (E-book)

Un aperçu approfondi de l'architecture AVR 8 bits présente dans les microcontrôleurs ATtiny et ATmega, principalement d'un point de vue logiciel et programmation. Explorez l'architecture AVR en utilisant le langage C et le langage assembleur dans Microchip Studio (anciennement Atmel Studio) avec les microcontrôleurs ATtiny. Apprenez les détails du fonctionnement interne des microcontrôleurs AVR, notamment les registres internes et la carte mémoire des microcontrôleur ATtiny. Programmez les microcontrôleurs ATtiny en utilisant un programmateur/débogueur Atmel-ICE, ou utilisez un programmateur "maison" bon marché, ou même un Arduino Uno comme programmateur. La plupart des exemples de code peuvent être exécutés à l'aide du simulateur AVR de Microchip Studio. Apprenez à écrire des programmes pour les microcontrôleurs ATtiny en langage assembleur. Découvrez comment le langage assembleur est converti en instructions de code machine par le programme assembleur. Découvrez comment les programmes écrits en langage de programmation C se traduitsent en langage assembleur et finalement en instructions de code machine. Utiliser le débogueur Microchip Studio en combinaison avec un programmateur/débogueur USB matériel pour tester les programmes en langage assembleur et langage C ou utiliser le simulateur AVR Microchip Studio. Les microcontrôleurs ATtiny en boîtier DIP sont utilisés dans ce volume pour une exploitation facile sur des platine d'essai électroniques, en ciblant principalement les ATtiny13(A) et ATtiny25/45/85. Comprenez la synchronisation des instructions et les horloges des microcontrôleurs AVR en utilisant les microcontrôleurs ATtiny. Devenez un expert AVR avec des compétences avancées en débogage et en programmation.

€ 34,95

Membres € 27,96

-

Espressif ESP32-WROOM-32D

L'ESP32-WROOM-32, mesurant uniquement 25,2 mm x 18 mm, contient le SoC ESP32, une mémoire flash, des composants discrets de précision et une antenne PCB pour offrir des performances RF exceptionnelles dans les applications limitées en espace. ESP32-WROOM-32 est un puissant module MCU Wi-Fi + BT + BLE générique qui cible une grande variété d'applications, allant des réseaux de capteurs basse consommation aux tâches les plus exigeantes, telles que l'encodage vocal, le streaming de musique et le décodage MP3. Au cœur de ce module se trouve la puce ESP32-D0WDQ6. La puce intégrée est conçue pour être évolutive et adaptative. Il existe deux cœurs de processeur qui peuvent être contrôlés individuellement et la fréquence d'horloge est réglable de 80 MHz à 240 MHz. L'utilisateur peut également éteindre le processeur et utiliser le coprocesseur basse consommation pour surveiller en permanence les périphériques en cas de changement ou de franchissement de seuils. L'ESP32 intègre un riche ensemble de périphériques, allant des capteurs tactiles capacitifs aux capteurs Hall, en passant par l'interface de carte SD, Ethernet, SPI haut débit, UART, I²S et I²C. L'intégration de Bluetooth, Bluetooth LE et Wi-Fi garantit qu'un large éventail d'applications peut être ciblée et que le module est à l'épreuve du temps. L'utilisation du Wi-Fi permet une vaste portée physique et une connexion directe à Internet via un routeur Wi-Fi, tandis que l'utilisation du Bluetooth permet à l'utilisateur de se connecter facilement au téléphone ou de diffuser des balises à faible consommation d'énergie pour sa détection. Le courant de veille de la puce ESP32 est inférieur à 5 µA, ce qui la rend adaptée aux applications électroniques alimentées par batterie et portables. L'ESP32 prend en charge un débit de données allant jusqu'à 150 Mbps et une puissance de sortie de 20,5 dBm au niveau de l'antenne pour garantir la plage physique la plus large. En tant que telle, la puce offre des spécifications de pointe et les meilleures performances en termes d'intégration électronique, de portée, de consommation d'énergie et de connectivité. Téléchargements Datasheet

€ 9,95€ 3,98

Membres identique

-

Espressif ESP32-S2-WROVER

Au cœur de ce module se trouve l'ESP32-S2, un processeur Xtensa® LX7 32 bits qui fonctionne jusqu'à 240 MHz. La puce dispose d'un coprocesseur basse consommation qui peut être utilisé à la place du processeur pour économiser de l'énergie tout en effectuant des tâches qui ne nécessitent pas beaucoup de puissance de calcul, comme la surveillance des périphériques. L'ESP32-S2 intègre un riche ensemble de périphériques, allant de SPI, I²S, UART, I²C, LED PWM, TWAITM, LCD, interface caméra, ADC, DAC, capteur tactile, capteur de température, ainsi que jusqu'à 43 GPIO. Il comprend également une interface USB On-The-Go (OTG) pleine vitesse pour permettre la communication USB. Caractéristiques MCU ESP32-S2 intégré, microprocesseur Xtensa® monocœur LX7 32 bits, jusqu'à 240 MHz ROM de 128 Ko 320 Ko de mémoire SRAM 16 Ko de SRAM en RTC Wifi 802.11b/g/n Débit binaire : 802.11n jusqu'à 150 Mbps Agrégation A-MPDU et A-MSDU Prise en charge de l'intervalle de garde de 0,4 µs Plage de fréquence centrale du canal opérationnel : 2 412 ~ 2 484 MHz Matériel Interfaces : GPIO, SPI, LCD, UART, I²C, I²S, interface caméra, IR, compteur d'impulsions, LED PWM, TWAI (compatible ISO 11898-1), USB OTG 1.1, ADC, DAC, capteur tactile, capteur de température Oscillateur à cristal de 40 MHz Flash SPI de 4 Mo Tension de fonctionnement/Alimentation : 3,0 ~ 3,6 V Plage de température de fonctionnement : –40 ~ 85 °C Dimensions : 18 × 31 × 3,3 mm Applications Hub de capteurs IoT générique à faible consommation Enregistreurs de données IoT génériques à faible consommation Caméras pour le streaming vidéo Appareils par contournement (OTT) Périphériques USB Reconnaissance de la parole Reconnaissance d'images Réseau maillé Automatisation de la maison Panneau de contrôle de maison intelligente Bâtiment intelligent L'automatisation industrielle Agriculture intelligente Applications audio Applications de soins de santé Jouets compatibles Wi-Fi Électronique portable Applications de vente au détail et de restauration Machines de point de vente intelligentes

€ 7,95€ 3,18

Membres identique

-

Espressif Kit ESP32-PICO

Dotée d’un minimum de composants discrets, la carte ESP32-PICO-KIT est entièrement fonctionnelle et expose toutes les broches de l’ESP32. Elle trouvera sa place sur la plus petite des plaques d’essai. Deux cœurs et une interface radio Comme l’ESP8266, l’ESP32 possède une interface Wi-Fi mais y ajoute le Bluetooth. Ses deux cœurs à 32 bits lui confèrent une énorme puissance, l’ESP32 fournissant de surcroît les ports et interfaces dont l’ESP8266 est dépourvu. Pour simplifier à l’extrême, l’ESP8266 est un contrôleur Wi-Fi doté de quelques E/S, alors que l’ESP32 est également un contrôleur Wi-Fi, mais complet. Périphériques ESP32 L’ESP32 comporte deux convertisseurs A/N et N/A, des circuits pour capteur tactile, un contrôleur hôte SD/SDIO/MMC, un contrôleur esclave SDIO/SPI, des interfaces UART, SPI, I²C, I²S, Ethernet MAC, MLI (PWM) pour la commande de LED et de moteurs, ainsi qu’une interface pour télécommande à infrarouge et, bien sûr, des ports GPIO. Carte de développement ESP32-PICO-KIT Le système sur puce (SoC) ESP32-PICO-D4 comprend une puce ESP32 et offre 4 Mo de mémoire flash SPI dans un petit boîtier de 7 x 7 mm. L’ESP32-PICO-KIT est sa carte de liaison. Elle embarque un convertisseur USB-série facilitant la programmation et le débogage. Outre la carte, vous aurez besoin d’une chaîne de programmation. Vous trouverez sur le site Read the Docs d’Espressif une documentation complète (en anglais) et à jour. Les instructions et commandes qui y sont décrites fonctionnent comme attendu. En plus de l’indispensable guide de démarrage, le site propose quantité d’informations utiles, notamment sur le matériel et l’API. Vous pouvez développer des applications pour l’ESP32-PICO-KIT sous Windows, Linux ou Ma

€ 19,95€ 7,98

Membres identique

-

Elektor Academy Pro ESP32 by Example (Cours d'apprentissage)

Cours complet sur le microcontrôleur ESP32, comprenant une carte d’extension MCU spécialement conçue, des projets pratiques et un guide en ligne complet – idéal pour apprendre le matériel, la programmation et la connectivité étape par étape. Introduction pratique aux systèmes embarqués avec l'ESP32 Ce cours est conçu pour les débutants en systèmes embarqués qui recherchent une approche structurée et concrète pour se lancer. Si vous avez déjà exploré l'électronique générale ou les ressources basées sur Arduino, mais que vous les avez trouvées trop générales ou manquant de conseils pratiques, ce cours offre une alternative plus ciblée. Grâce au kit « ESP32 by Example » (EEK) – un ensemble de composants compacts et abordables comprenant des LED, des capteurs, un écran OLED et un processeur de mouvement – vous travaillerez avec une configuration matérielle cohérente tout au long du cours. Une fois assemblé, l'EEK reste quasiment inchangé, ce qui vous permet de vous concentrer sur l'apprentissage et l'expérimentation sans reconfiguration constante. Sujets abordés : Comprendre et programmer le microcontrôleur ESP32 Écrire et déployer du code avec l’IDE Arduino Explorer les systèmes cyberphysiques, jusqu’au pilotage de drones de base Aucune expérience préalable avec Arduino ou le développement embarqué n’est requise. Chaque section propose des exemples pratiques et des mini-projets conçus pour consolider les concepts clés et encourager une exploration plus approfondie. À la fin de ce cours, vous serez capable non seulement de reproduire les exemples du livre, mais aussi de les enrichir avec vos propres idées et applications. Que vous soyez intéressé par la programmation embarquée, les systèmes interactifs ou le pilotage de drones, ce cours vous offre une approche claire et pratique pour débuter. Ce que vous apprendrez ? Programmation embarquée avec l'ESP32 à l'aide de l'IDE Arduino Acquisition et contrôle en temps réel des données de capteurs via boutons, LED et écrans Interaction gestuelle grâce au capteur de mouvement MPU6050 Intégration d'une manette de jeu Bluetooth et simulation de contrôle de drone Réseaux Wi-Fi et UDP, serveurs web locaux et NTP Communication MQTT avec des plateformes cloud telles qu'AWS et Arduino IoT Comment concevoir et déployer des systèmes IoT complets Idéal pour Étudiants et autodidactes explorant les systèmes embarqués Créateurs et passionnés d'IoT souhaitant perfectionner leurs compétences en matériel Enseignants et formateurs à la recherche de ressources pédagogiques prêtes à l'emploi Développeurs souhaitant aller au-delà des bases de Raspberry Pi ou Arduino Une assistance en cas de besoin Accès aux formateurs via Elektor Academy Forums communautaires utiles et documentation essentielle Que contient la boîte (cours) ? Nouveau livre de 384 pages : « ESP32 by Example » (valeur : 45 €) Kit Elektor ESP32 by Example (EEK) : Carte d’extension pour microcontrôleur avec 6 LED et 6 boutons intégrés + écran OLED, module accéléromètre et gyroscope 3 axes MPU6050 (valeur : 40 €) Carte Adafruit HUZZAH32 – ESP32 Feather MCU (valeur : 30 €) Carte ESP32 Cheap Yellow Display (valeur : 25 €) Capteur d’humidité et de température DHT11 Plaque d'essai Câbles de connexion Câble USB-C Accès au cours complet sur la plateforme d'apprentissage Elektor Academy Pro Vidéos pédagogiques Fichiers de projet Arduino téléchargeables pour chaque module Matériel pédagogique (de cette boîte/ce cours) ▶ Cliquez ici pour ouvrir Module 1 – Getting Started with the ESP32 & EEK Module 2 – Digital Output – LEDs and GPIO Module 3 – Switches and Input Handling Module 4 – EEK and PWM Module 5 – OLED and Display Output Module 6 – Motion Sensing with the MPU6050 Module 7 – Capstone Project (EEK in Action) Module 8 – WiFi and Web Control with ESP32 Module 9 – Cloud Concepts using EEK Module 10 – Hands-on: Arduino IoT Cloud and EEK Module 11 – BlueTooth and EEK GamePad Integration Module 12 – Why Drones? Module 13 – Drone Simulator Concepts Module 14 – Simple Drone Flight Control Module 15 – Real-Time Drone Flight Control Module 16 – Drone Control Mini-Projects Module 17 – Middleware and Python Scripting Module 18 – Python Applications for Drone Control Module 19 – Capstone EEK Control Project and Presentation À propos de l'auteur Jim Solderitsch est un enseignant, architecte logiciel, développeur de systèmes et chercheur en cybersécurité spécialisé dans les systèmes cyberphysiques. Il est actuellement professeur associé en sciences informatiques à l'Villanova University en Pennsylvanie. Qu'est-ce qu'Elektor Academy Pro ? Elektor Academy Pro propose des solutions d’apprentissage spécialisées, conçues pour les professionnels, les équipes d’ingénieurs et les experts techniques du secteur de l’électronique et des systèmes embarqués. Elle permet aux individus et aux organisations d’approfondir leurs connaissances pratiques, de perfectionner leurs compétences et de garder une longueur d’avance grâce à des ressources de haute qualité et des outils de formation concrets. Des projets réels aux formations animées par des spécialistes, en passant par des analyses techniques approfondies, Elektor donne aux ingénieurs les moyens de relever les défis actuels du secteur. Notre offre de formation inclut des livres Academy, des coffrets Pro, des webinaires, des conférences et des magazines B2B spécialisés – tous conçus pour favoriser le développement professionnel. Que vous soyez ingénieur, expert R&D ou décideur technique, Elektor Academy Pro fait le lien entre la théorie et la pratique, vous aide à maîtriser les technologies émergentes et à faire progresser l’innovation dans votre entreprise.

€ 269,00€ 219,00

Membres identique

-

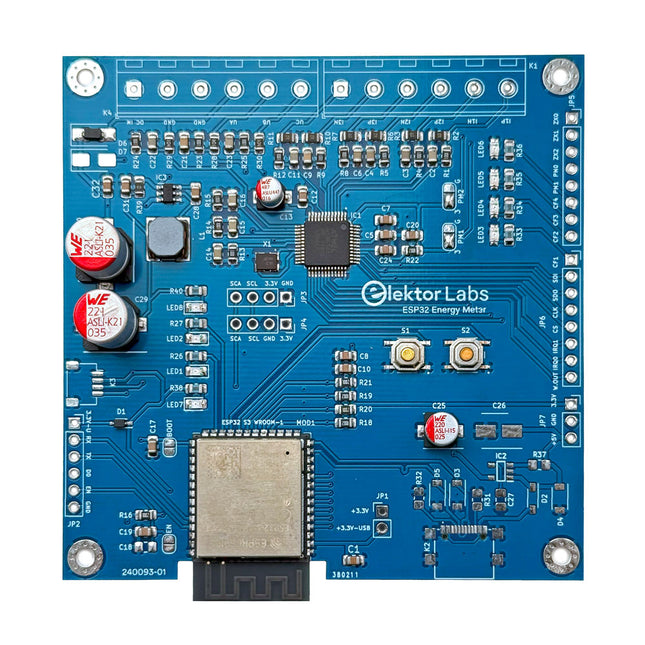

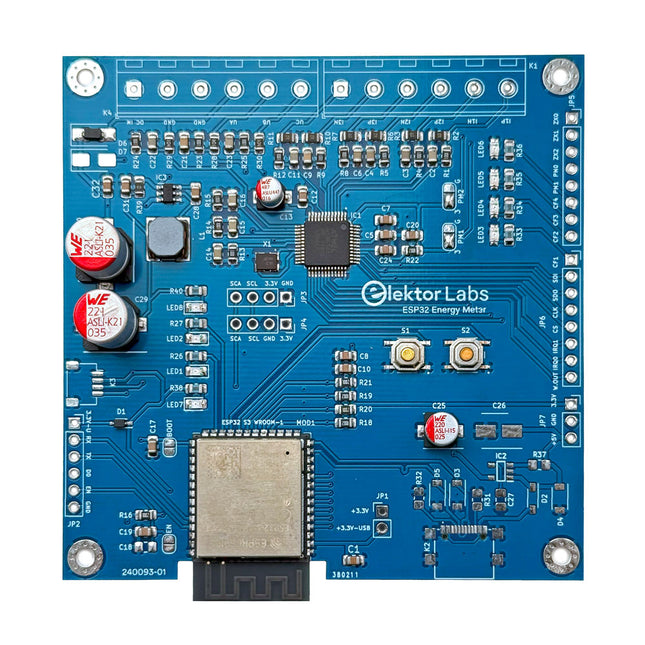

Elektor Labs Compteur d'énergie ESP32 Elektor

Le compteur d'énergie Elektor ESP32 est un appareil conçu pour la surveillance de l'énergie en temps réel et l'intégration de la maison connectée. Alimenté par le microcontrôleur ESP32-S3, il offre des performances robustes avec des fonctionnalités modulaires et évolutives. L'appareil utilise un transformateur abaisseur de 220 V à 12 V pour l'échantillonnage de tension, garantissant ainsi l'isolation galvanique et la sécurité. Sa configuration PCB compacte comprend des borniers à vis pour des connexions sécurisées, un connecteur Qwiic pour des capteurs supplémentaires et un connecteur de programmation pour une configuration directe ESP32-S3. Le compteur d'énergie est compatible avec les systèmes monophasés et triphasés, ce qui le rend adaptable à diverses applications. Le compteur d'énergie est simple à configurer et s'intègre à Home Assistant, offrant des capacités de surveillance en temps réel, d'analyse historique et d'automatisation. Il fournit des mesures précises de tension, de courant et de puissance, ce qui en fait un outil précieux pour la gestion de l'énergie dans les maisons et les entreprises. Caractéristiques Surveillance complète de l'énergie : Obtenez des informations détaillées sur votre consommation d'énergie pour une gestion plus intelligente. Logiciel personnalisable : Adaptez les fonctionnalités à vos besoins en programmant et en intégrant des capteurs personnalisés. Prêt pour la maison connectée : Compatible avec ESPHome, Home Assistant et MQTT pour une intégration complète à la maison connectée. Conception sûre et flexible : Fonctionne avec un transformateur abaisseur de 220 V à 12 V et comporte une carte CMS pré-assemblée. Démarrage rapide : Comprend un capteur de transformateur de courant et un accès à des ressources de configuration gratuites. Spécifications Microcontrôleur ESP32-S3-WROOM-1-N8R2 CI de mesure d'énergie ATM90E32AS Indicateurs d'état 4 LED pour l'indication de la consommation électrique2 LED programmables pour les notifications d'état personnalisées Entrée utilisateur 2x boutons-poussoirs pour le contrôle utilisateur Afficher la sortie Écran OLED I²C pour une visualisation de la consommation électrique en temps réel Tension d'entrée 110/220 V AC (via transformateur abaisseur) Puissance d'entrée 12 V (via transformateur abaisseur ou entrée DC) Capteur de courant à pince YHDC SCT013-000 (100 A/50 mA) inclus Intégration de la maison connectée ESPHome, Home Assistant et MQTT pour une connectivité transparente Connectivité En-tête pour la programmation, Qwiic pour l'extension du capteur Applications Prend en charge les systèmes de surveillance de l'énergie monophasés et triphasés Dimensions 79,5 x 79,5 mm Inclus 1x Carte partiellement assemblée (les composants CMS sont pré-montés) 2x Connecteurs de bornier à vis (non montés) 1x Transformateur de courant YHDC SCT013-000 Requis Transformateur de puissance non inclus Téléchargements Datasheet (ESP32-S3-WROOM-1) Datasheet (ATM90E32AS) Datasheet (SCT013-000) Frequently Asked Questions (FAQ) Du prototype au produit fini Ce qui a commencé comme un projet innovant visant à créer un compteur d'énergie fiable et convivial utilisant le microcontrôleur ESP32-S3 est devenu un produit robuste. Initialement développé en tant que projet open source, le compteur d'énergie ESP32 visait à fournir une surveillance précise de l'énergie, une intégration de maison intelligente et bien plus encore. Grâce à un développement méticuleux du matériel et du micrologiciel, le compteur d'énergie se présente désormais comme une solution compacte et polyvalente pour la gestion de l'énergie.

€ 79,95€ 64,95

Membres identique

-

Espressif ESP32-S2-WROOM

Au cœur de ce module se trouve l'ESP32-S2, un processeur Xtensa® LX7 32 bits qui fonctionne jusqu'à 240 MHz. La puce dispose d'un coprocesseur basse consommation qui peut être utilisé à la place du processeur pour économiser de l'énergie tout en effectuant des tâches qui ne nécessitent pas beaucoup de puissance de calcul, comme la surveillance des périphériques. L'ESP32-S2 intègre un riche ensemble de périphériques, allant de SPI, I²S, UART, I²C, LED PWM, TWAITM, LCD, interface caméra, ADC, DAC, capteur tactile, capteur de température, ainsi que jusqu'à 43 GPIO. Il comprend également une interface USB On-The-Go (OTG) pleine vitesse pour permettre la communication USB. Caractéristiques MCU ESP32-S2 intégré, microprocesseur Xtensa® monocœur LX7 32 bits, jusqu'à 240 MHz ROM de 128 Ko 320 Ko de mémoire SRAM 16 Ko de SRAM en RTC Wifi 802.11b/g/n Débit binaire : 802.11n jusqu'à 150 Mbps Agrégation A-MPDU et A-MSDU Prise en charge de l'intervalle de garde de 0,4 µs Plage de fréquence centrale du canal opérationnel : 2 412 ~ 2 484 MHz Matériel Interfaces : GPIO, SPI, LCD, UART, I²C, I²S, interface caméra, IR, compteur d'impulsions, LED PWM, TWAI (compatible ISO 11898-1), USB OTG 1.1, ADC, DAC, capteur tactile, capteur de température Oscillateur à cristal de 40 MHz Flash SPI de 4 Mo Tension de fonctionnement/Alimentation : 3,0 ~ 3,6 V Plage de température de fonctionnement : –40 ~ 85 °C Dimensions : 18 × 31 × 3,3 mm Applications Hub de capteurs IoT générique à faible consommation Enregistreurs de données IoT génériques à faible consommation Caméras pour le streaming vidéo Appareils par contournement (OTT) Périphériques USB Reconnaissance de la parole Reconnaissance d'images Réseau maillé Automatisation de la maison Panneau de contrôle de maison intelligente Bâtiment intelligent L'automatisation industrielle Agriculture intelligente Applications audio Applications de soins de santé Jouets compatibles Wi-Fi Électronique portable Applications de vente au détail et de restauration Machines de point de vente intelligentes

€ 6,95€ 2,78

Membres identique